Computer Architecture Essentials

Cheatsheet Content

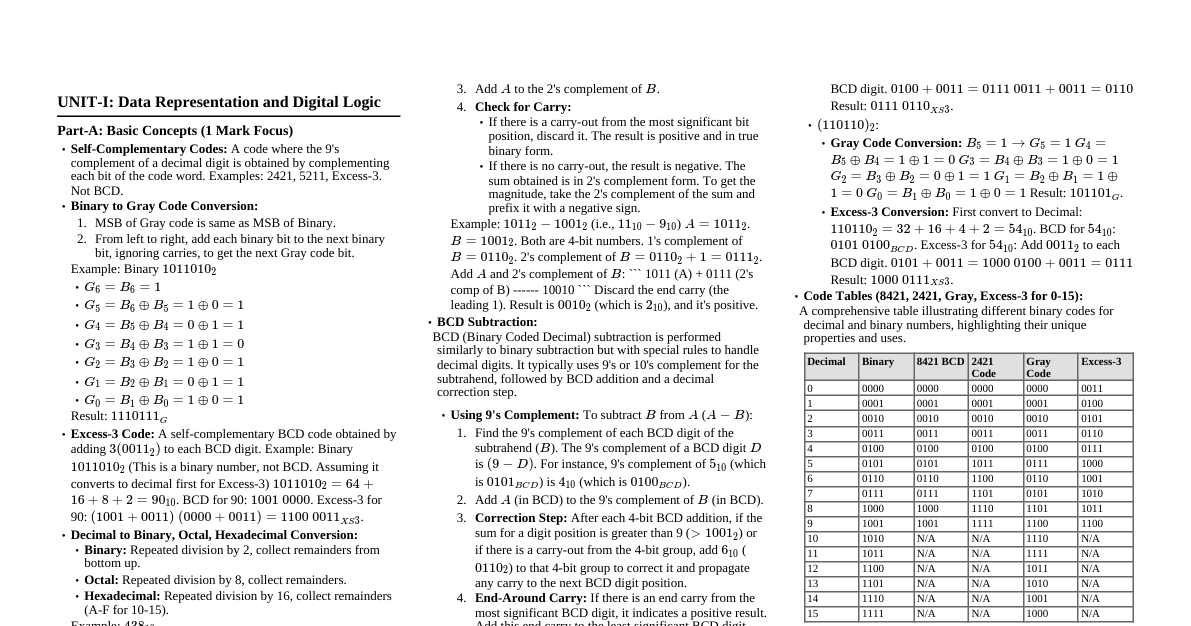

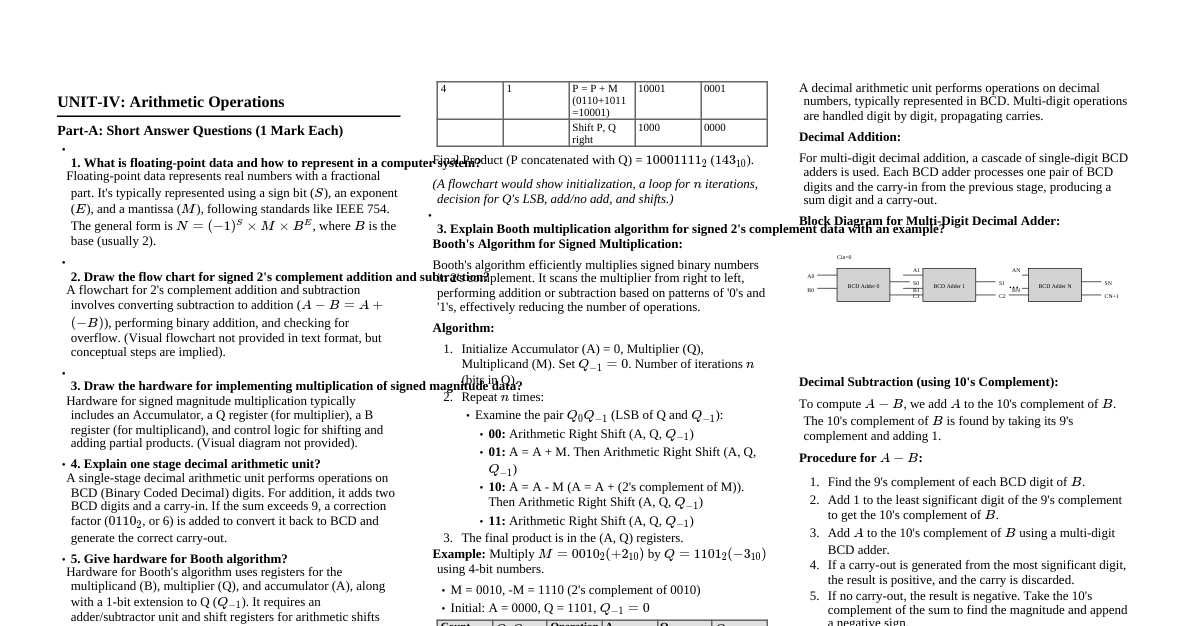

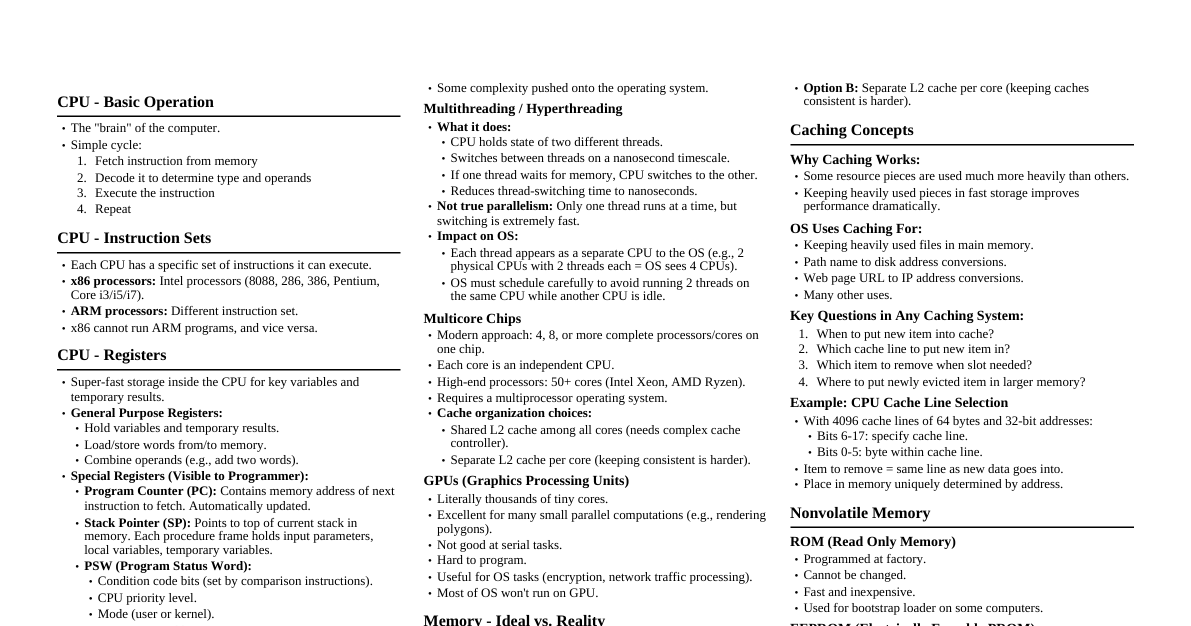

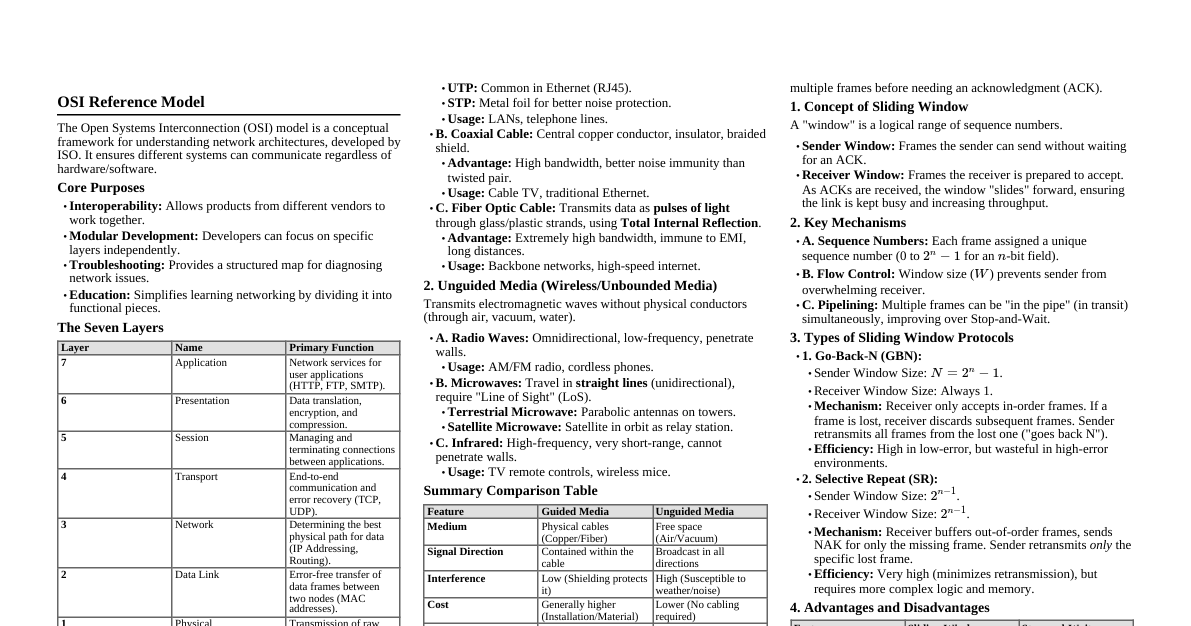

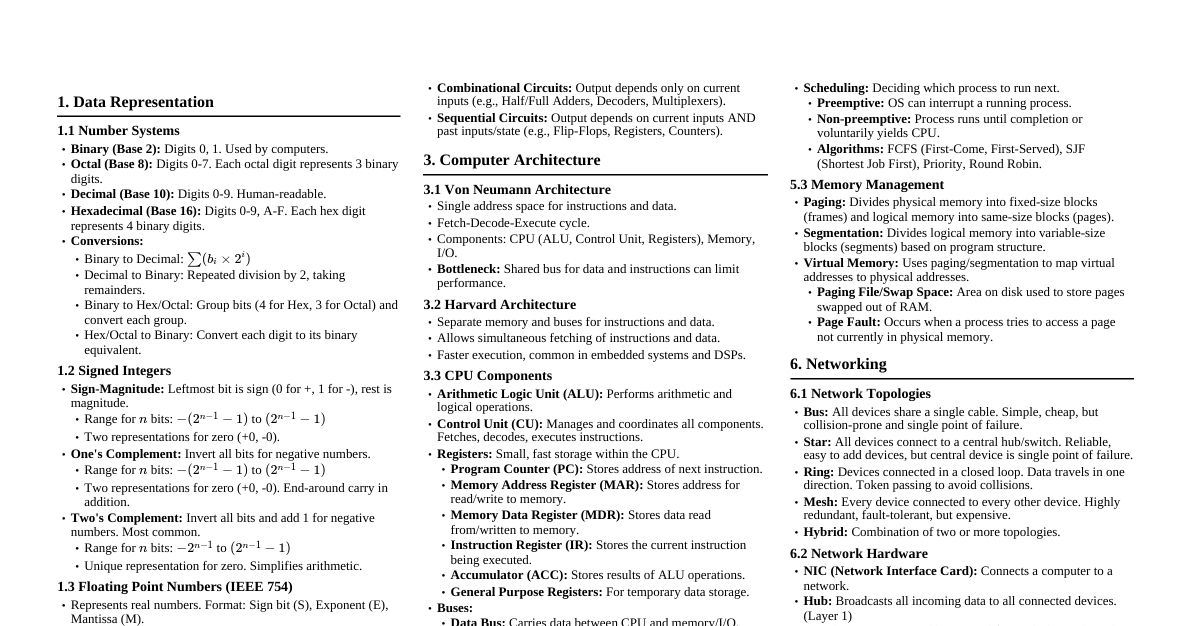

Clocking Methodology Defines when signals can be read and written. Two types: Edge-triggered clocking: Allows reading register contents, sending value through combinational logic, and writing to the register in the same clock cycle. Combinational logic: Operates in a single clock cycle. MIPS Instruction Set Memory reference instruction: lw , sw (load word, store word) Arithmetic logical instruction: add , sub , and , or , sll (add, subtract, logical AND, logical OR, shift left logical) Branch instruction: beq , j (branch if equal, jump) All instruction classes use the ALU after reading the registers: Memory reference: Address calculation Arithmetic logic: Operation execution Branch: Comparison Datapath A set of functional units that carry out data processing operations. It is a unit to operate on one-word data within a processor. A larger datapath can be made by joining more than one datapath using multiplexers. Components of Datapath: Instruction and data memories Register file ALU (Arithmetic Logic Unit) Address Single Cycle Datapath Operation (R-type): The instruction is fetched and the PC is incremented. Two registers, $s1 , $s2 , and $s3 , are read from the register file. The main control unit computes the setting of the control lines. The ALU operates on the data read from the register file using the function code to generate ALU function. The result from the ALU is written into the register file using bits 15-11 of the instruction to select the destination register ( $s3 ). Operation (J-type): The instruction is fetched from the instruction memory and the PC is incremented. A register ( $s2 ) value is read from the register file. The ALU computes the sum of the value read from the register file, operates on the data from the register file, and sign-extended, lower 16 bits of the instruction (offset). The sum from the ALU is used as the address for the data memory. Why a single cycle implementation is not used? It is inefficient. The length of the clock cycle will always be determined by the slowest operation ( lw , sw ) even if the data memory is not used. Practical implementations use multiple cycles per instruction, which fixes some shortcomings of the 1-cycle implementation. Multicycle Datapath Advantages of multicycle datapath implementation over single cycle: A single memory unit is used for both instruction and data. There is a single ALU, rather an ALU and two address. One or more registers are added after every major functional unit to hold the output of that unit until the value is used in a subsequent clock cycle. The clock cycle can be much shorter. Can require less hardware. Can eliminate two adders. Exceptions An exception is an unexpected event from within the processor. Types: Due to an undefined instruction. An arithmetic overflow. How exceptions are handled: The two types of exceptions that our current implementation can generate are an exception of an undefined instruction and an arithmetic overflow. The operating system can then take the appropriate action, which may involve providing some service to the user program.