Flip-Flop Essentials

Cheatsheet Content

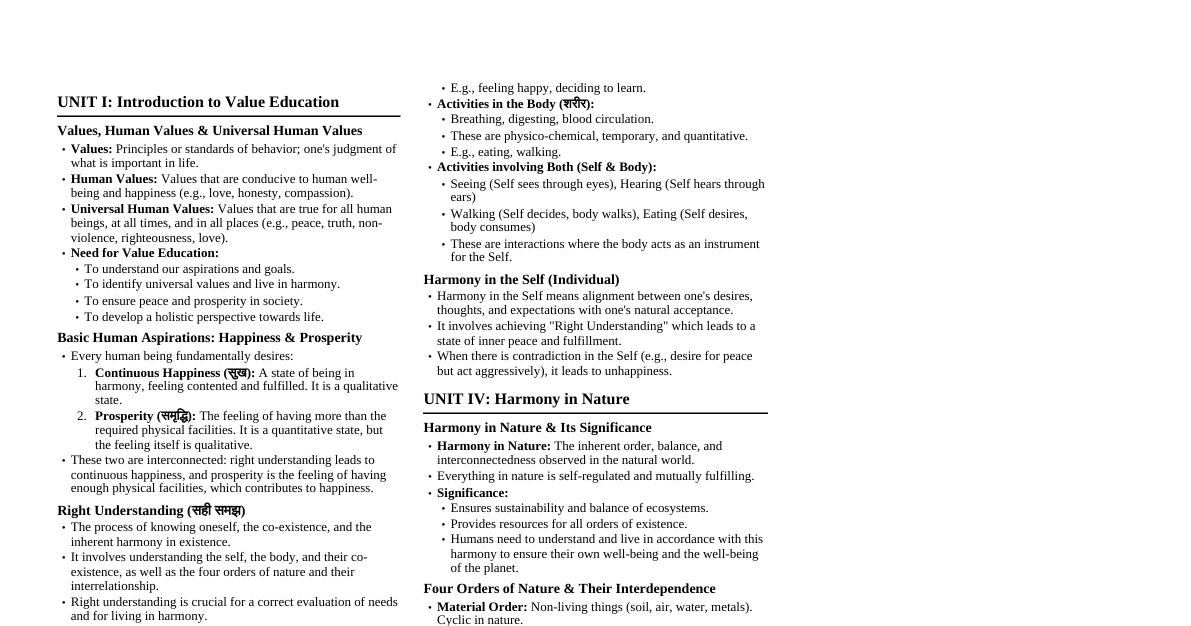

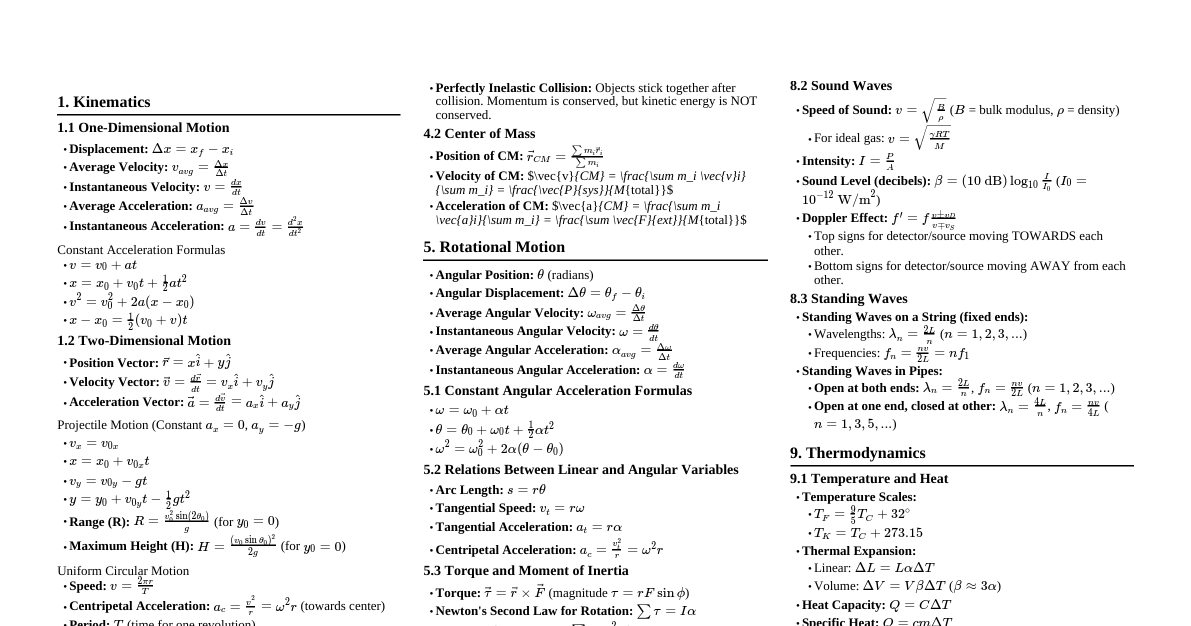

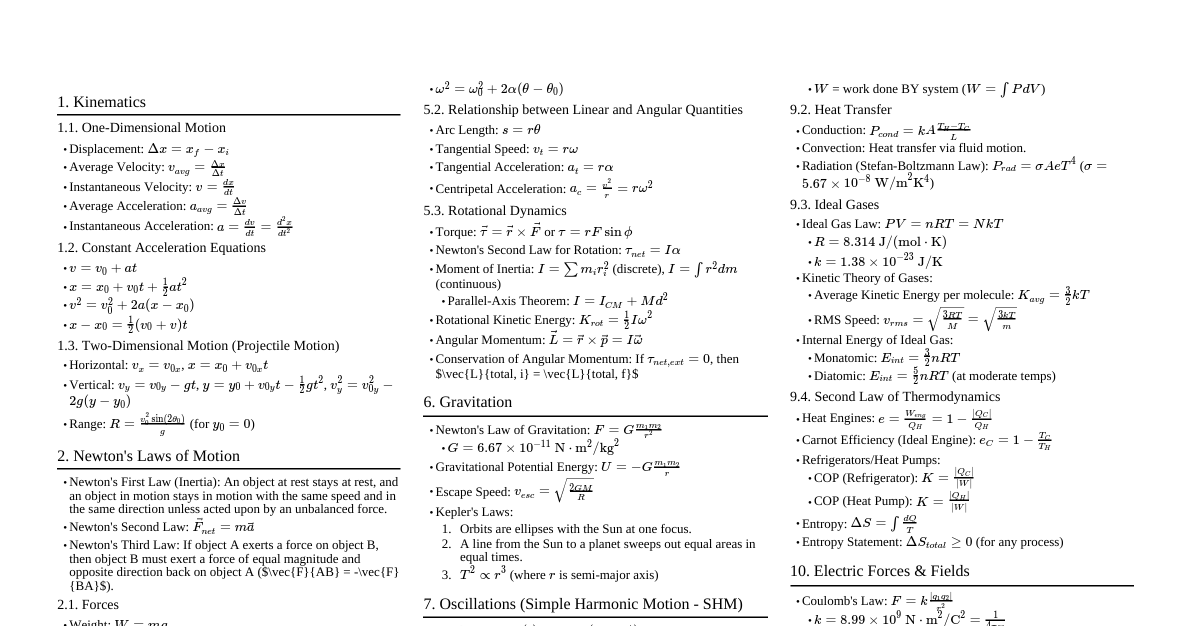

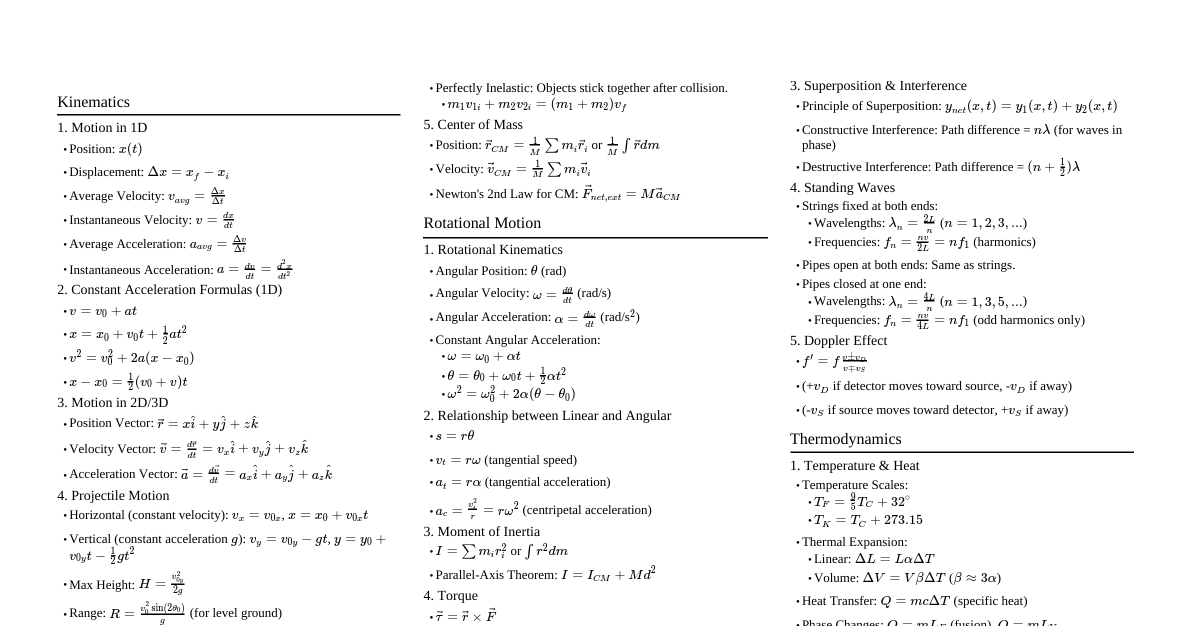

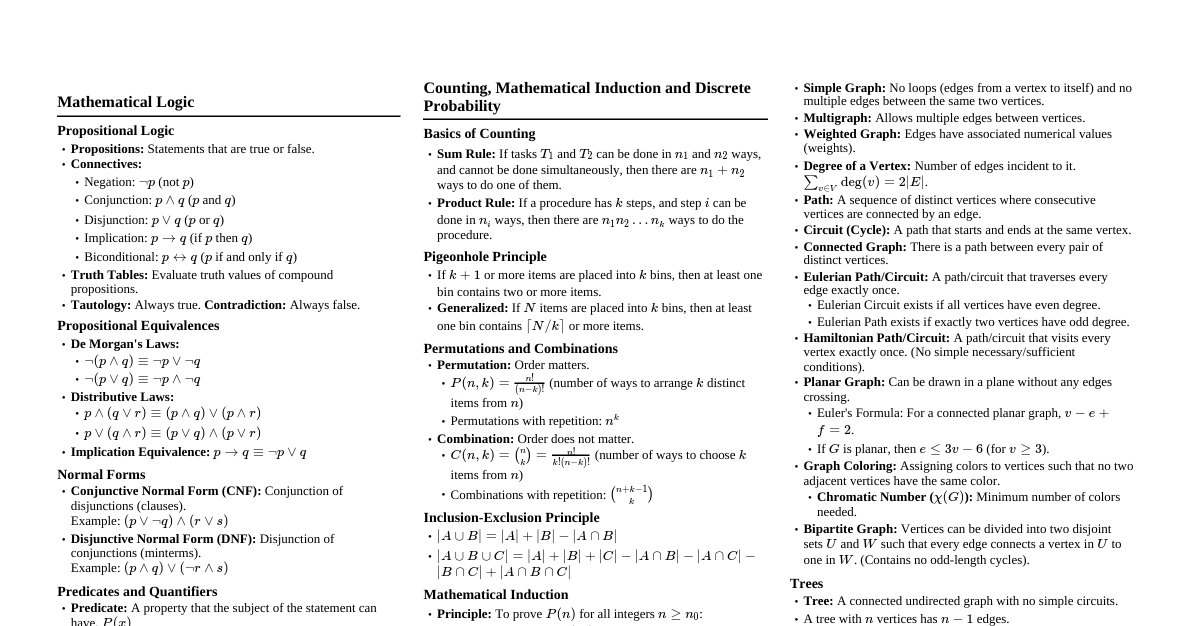

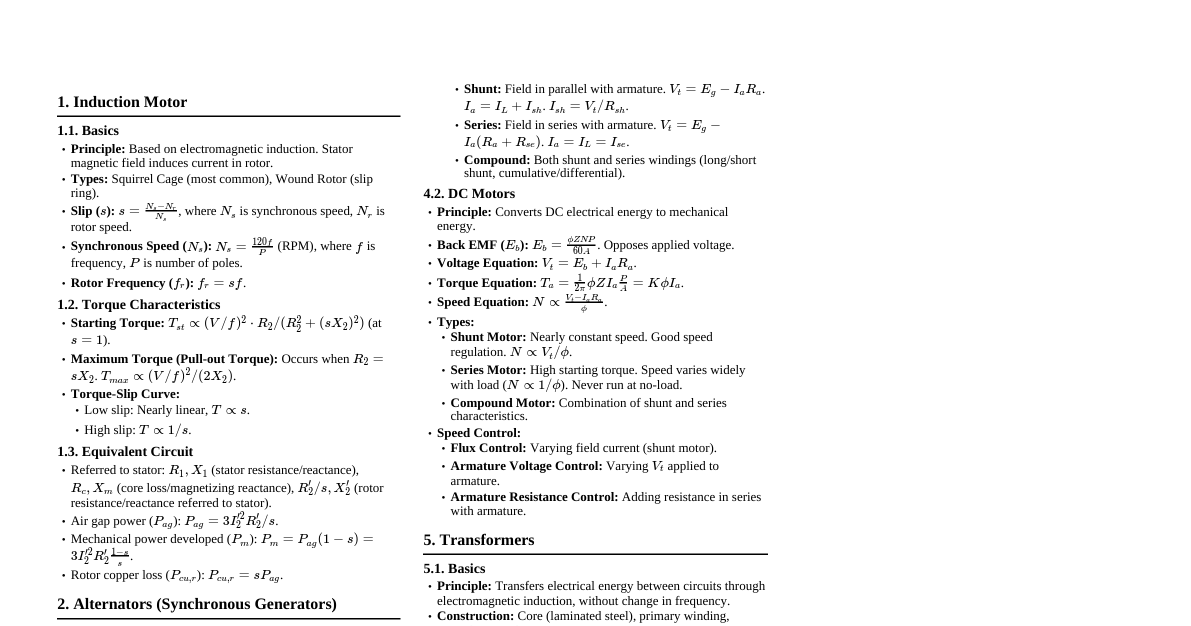

Sequential Logic Basics Sequential Logic: Output depends on current inputs AND past inputs (memory). Combinational Logic: Output depends only on current inputs. Memory Element: Stores a binary value (0 or 1). Clock Signal ($CLK$): Synchronizes operations in sequential circuits. State: The current value stored in memory elements. Latches vs. Flip-Flops Latch: Level-sensitive. Output can change as long as the enable signal is active (high or low level). Level Triggering: Output responds to the input level (e.g., $E=1$) rather than a transition. Can lead to "transparency" where output follows input while enable is active. Flip-Flop: Edge-triggered. Output changes only at the rising or falling edge of the clock signal. Edge Triggering: Output responds only at the specific transition (edge) of the clock signal. Provides more precise control and avoids race conditions in synchronous systems. Example: Positive edge-triggered (changes on $0 \to 1$ clock transition), Negative edge-triggered (changes on $1 \to 0$ clock transition). Flip-flops are preferred for synchronous sequential circuits to prevent race conditions and ensure predictable behavior. SR Latch (Set-Reset Latch) NOR-based SR Latch Inputs: $S$ (Set), $R$ (Reset) Outputs: $Q$, $\bar{Q}$ Characteristic Table: $S$ $R$ $Q_{next}$ Comment 0 0 $Q_{prev}$ No Change 0 1 0 Reset 1 0 1 Set 1 1 Invalid Forbidden State Issue: $S=1, R=1$ leads to an undefined state. NAND-based SR Latch Active-low inputs ($\bar{S}, \bar{R}$). $S=0, R=0$ is the forbidden state. Gated SR Latch Adds an Enable (or Clock) input. Outputs change only when Enable is active. Still suffers from the $S=1, R=1$ forbidden state. D Latch (Data Latch) Resolves the forbidden state of SR latch. Inputs: $D$ (Data), $E$ (Enable) Outputs: $Q$, $\bar{Q}$ $S = D$, $R = \bar{D}$ (for NOR-based SR latch). Characteristic Table: $E$ $D$ $Q_{next}$ Comment 0 X $Q_{prev}$ No Change 1 0 0 Reset 1 1 1 Set Transparent Latch: When $E=1$, $Q$ follows $D$. This is why D latches are sometimes called "transparent latches". The input "shines through" to the output. D Flip-Flop (Data Flip-Flop) Most common type. Inputs: $D$ (Data), $CLK$ (Clock) Outputs: $Q$, $\bar{Q}$ Operation: $Q_{next} = D$ at the active clock edge (rising or falling). Characteristic Equation: $Q_{next} = D$ Excitation Table: $Q_t$ $Q_{t+1}$ $D$ 0 0 0 0 1 1 1 0 0 1 1 1 Used for registers, shift registers, counters. JK Flip-Flop Versatile, resolves SR flip-flop's invalid state. Inputs: $J$ (Set), $K$ (Reset), $CLK$ Outputs: $Q$, $\bar{Q}$ Characteristic Table: $J$ $K$ $Q_{next}$ Comment 0 0 $Q_{prev}$ No Change 0 1 0 Reset 1 0 1 Set 1 1 $\bar{Q}_{prev}$ Toggle Characteristic Equation: $Q_{next} = J\bar{Q} + \bar{K}Q$ Excitation Table: $Q_t$ $Q_{t+1}$ $J$ $K$ 0 0 0 X 0 1 1 X 1 0 X 1 1 1 X 0 Can be configured as SR, D, or T flip-flop. Master-Slave JK Flip-Flop A design to overcome the "race-around condition" in simple edge-triggered JK flip-flops. Consists of two cascaded JK latches: Master Latch: Enabled when $CLK=1$. It takes inputs $J, K$ and its output determines the state for the slave. Slave Latch: Enabled when $CLK=0$. It takes the master's output as its input. Operation: When $CLK=1$: Master is active, captures $J, K$. Slave is inactive, holds previous state. When $CLK$ goes $1 \to 0$: Master becomes inactive, holds its state. Slave becomes active, copies the master's state to its output $Q$. Effectively, data is transferred to the output only on the falling edge of the clock (or rising, depending on inversion). Race-Around Condition Occurs in simple (non-master-slave) JK flip-flops that are level-triggered (like a gated JK latch) or if the clock pulse width is too long for an edge-triggered design. When $J=1, K=1$ (toggle mode) and the clock pulse is high (for a positive level-triggered device), the output $Q$ toggles, then the new $Q$ feeds back to the input, causing it to toggle again, and so on, multiple times within the same clock pulse. The final output $Q$ becomes unpredictable. Solution: Using edge-triggered flip-flops or master-slave configurations. T Flip-Flop (Toggle Flip-Flop) Derived from JK flip-flop by connecting $J=K=T$. Inputs: $T$ (Toggle), $CLK$ Outputs: $Q$, $\bar{Q}$ Characteristic Table: $T$ $Q_{next}$ Comment 0 $Q_{prev}$ No Change 1 $\bar{Q}_{prev}$ Toggle Characteristic Equation: $Q_{next} = T\bar{Q} + \bar{T}Q = T \oplus Q$ Excitation Table: $Q_t$ $Q_{t+1}$ $T$ 0 0 0 0 1 1 1 0 1 1 1 0 Used in counters and frequency dividers. Asynchronous Inputs Preset (PR) / Set (S): Forces $Q=1$, overriding clock and synchronous inputs. Often active-low ($\overline{PR}$). Clear (CLR) / Reset (R): Forces $Q=0$, overriding clock and synchronous inputs. Often active-low ($\overline{CLR}$). These inputs are used for initialization. Timing Parameters Setup Time ($t_{su}$): Minimum time data ($D, J, K, T$) must be stable BEFORE the active clock edge. Hold Time ($t_h$): Minimum time data must be stable AFTER the active clock edge. Propagation Delay ($t_{pd}$): Time taken for the output ($Q$) to change after the active clock edge. $t_{pLH}$: Delay for output to go from Low to High. $t_{pHL}$: Delay for output to go from High to Low. Applications of Flip-Flops Registers: Store multiple bits of data (e.g., 8-bit register uses 8 D flip-flops). Counters: Count clock pulses (e.g., ripple counters, synchronous counters). Shift Registers: Move data bit by bit (serial-in/parallel-out, parallel-in/serial-out). Frequency Dividers: Divide the input clock frequency. State Machines: Fundamental building blocks of finite state machines (FSMs).